## Digital Design Lecture 8

Combinatorial Logic (Continued)

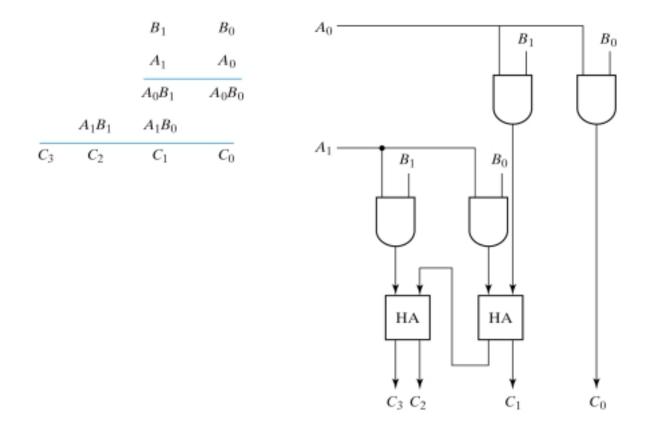

## Binary Multiplier: 2-bit by 2-bit

Fig. 4-15 2-Bit by 2-Bit Binary Multiplier

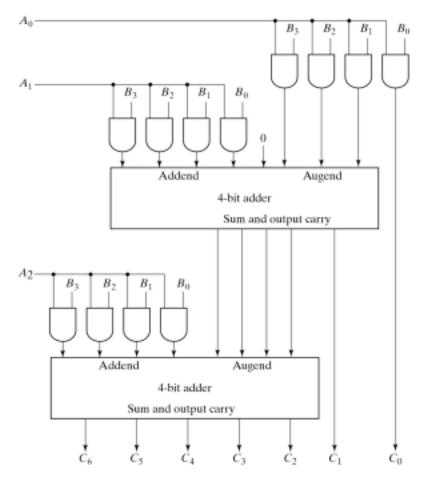

## Binary Multiplier: 4-bit by 3-bit

Fig. 4-16 4-Bit by 3-Bit Binary Multiplier

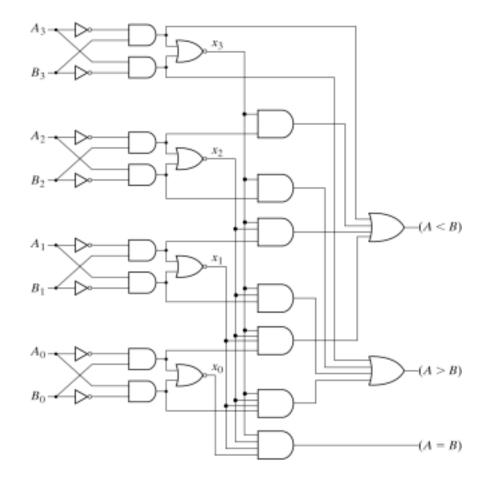

## 4-Bit Magnitude Comparator

Fig. 4-17 4-Bit Magnitude Comparator

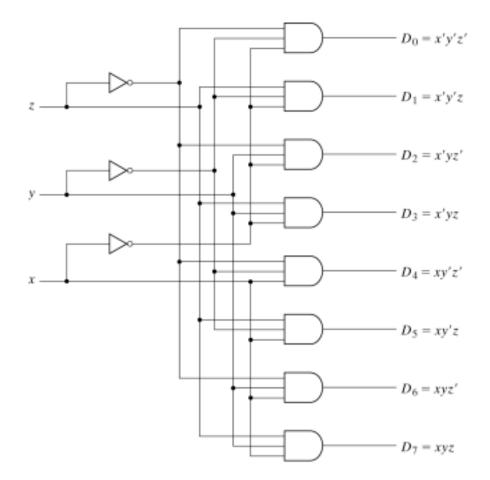

#### 3-to-8 Line Decoder

Fig. 4-18 3-to-8-Line Decoder

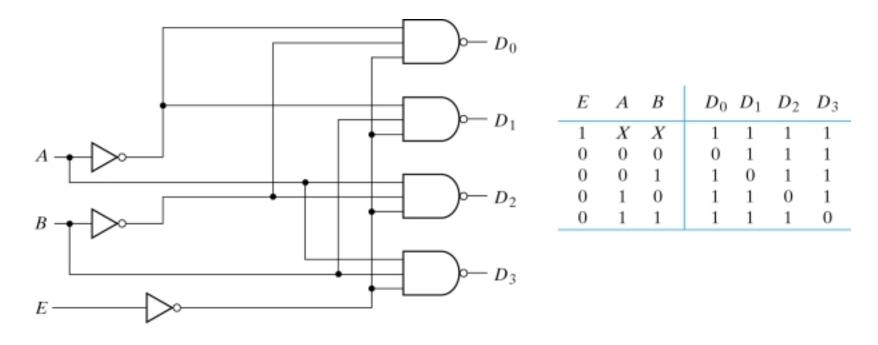

### 2-to-4 Line Decoder with Enable

(a) Logic diagram

(b) Truth table

Fig. 4-19 2-to-4-Line Decoder with Enable Input

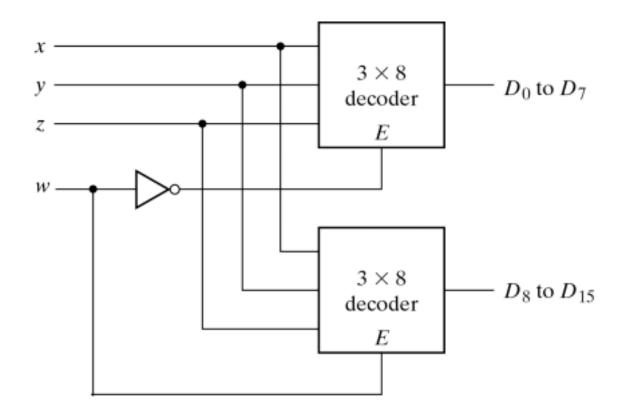

## **Building Large Decoders**

Fig. 4-20 4  $\times$  16 Decoder Constructed with Two 3  $\times$  8 Decoders

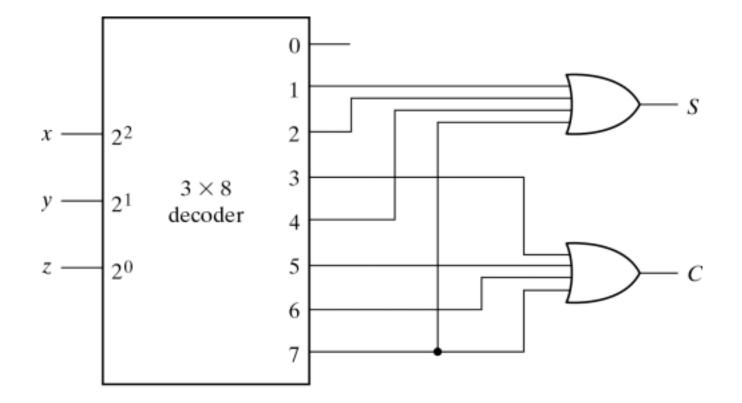

#### Full Adder Via a Decoder

Fig. 4-21 Implementation of a Full Adder with a Decoder

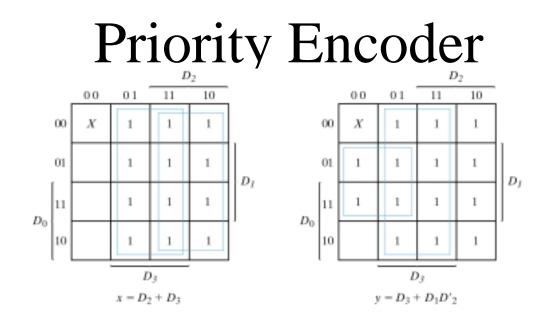

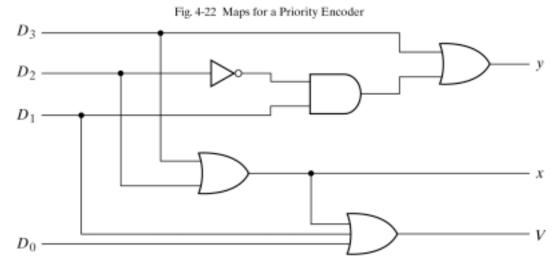

Fig. 4-23 4-Input Priority Encoder

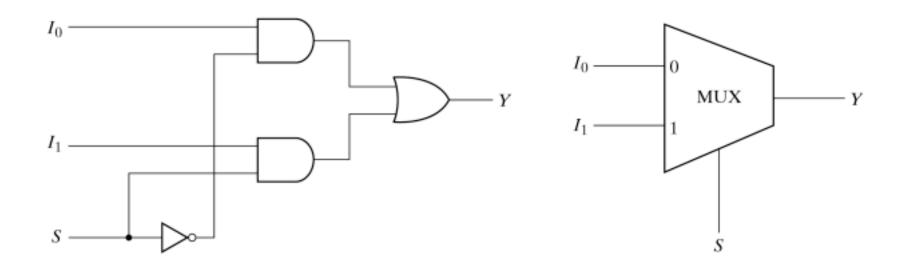

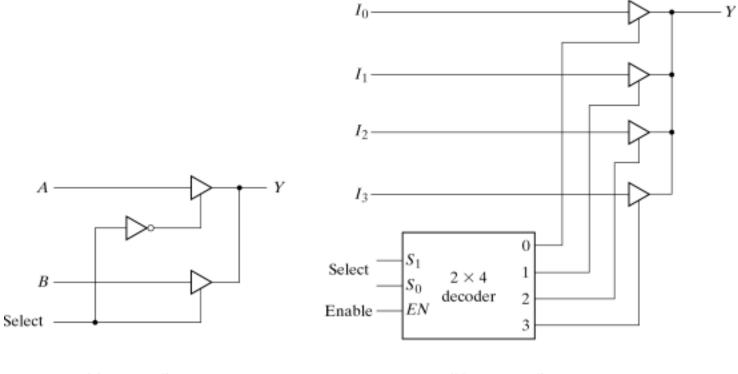

### 2-to-1 Line Multiplexer

(a) Logic diagram

(b) Block diagram

Fig. 4-24 2-to-1-Line Multiplexer

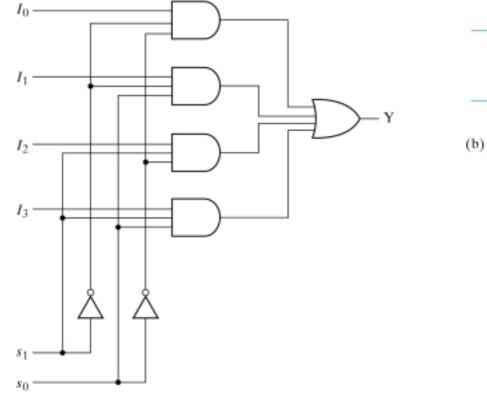

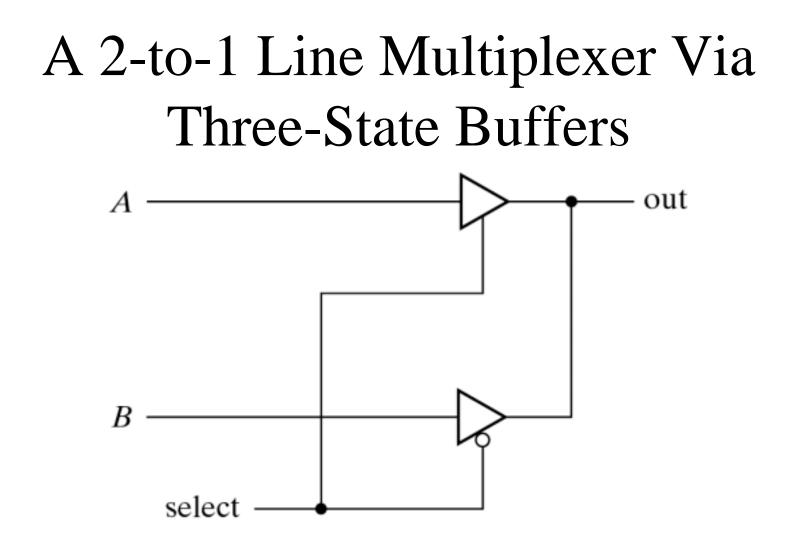

### 4-to-1 Line Multiplexer

| $s_1$ | $s_0$ | Y     |

|-------|-------|-------|

| 0     | 0     | $I_0$ |

| 0     | 1     | $I_1$ |

| 1     | 0     | $I_2$ |

| 1     | 1     | $I_3$ |

(b) Function table

(a) Logic diagram

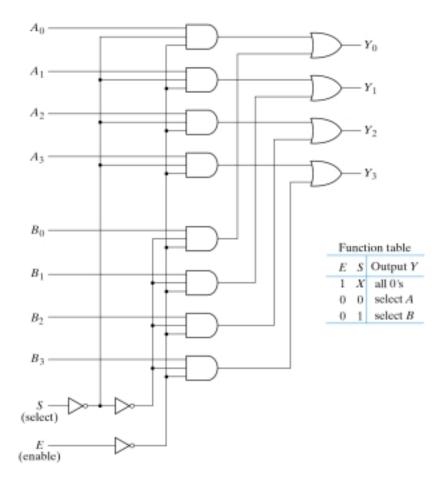

### 2-to-1 Line Multiplexer \* 4

Fig. 4-26 Quadruple 2-to-1-Line Multiplexer

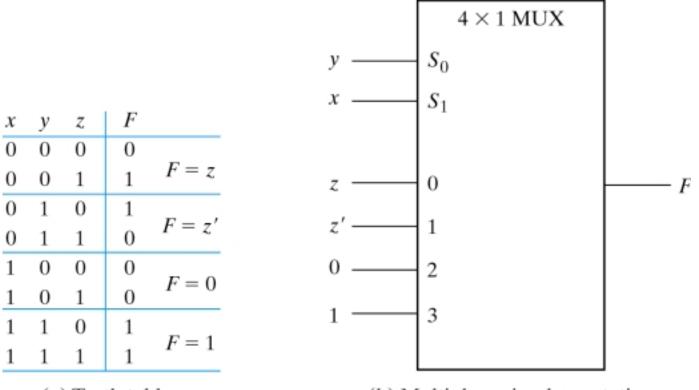

# Boolean Functions Via a Multiplexer

(a) Truth table

(b) Multiplexer implementation

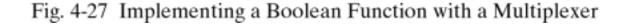

# A 4-Input Function Via a Multiplexer

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

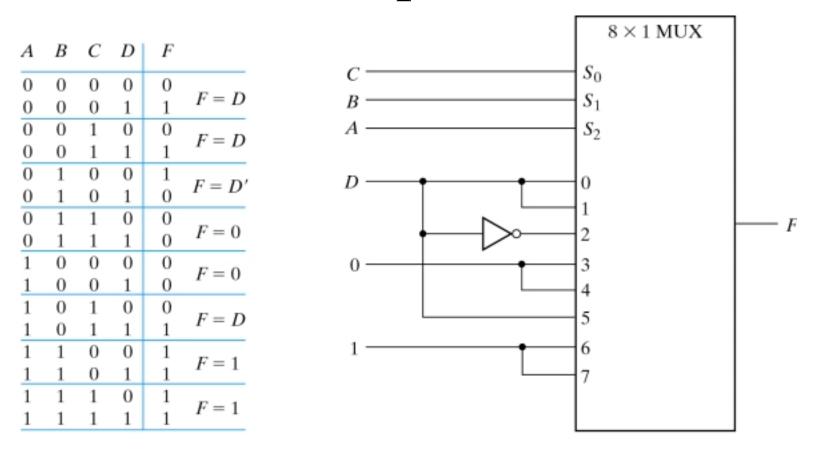

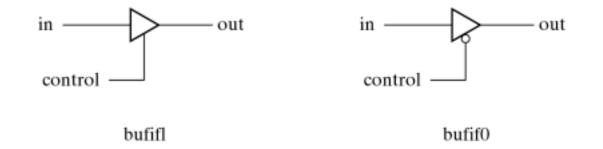

#### Three State Buffers

Fig. 4-29 Graphic Symbol for a Three-State Buffer

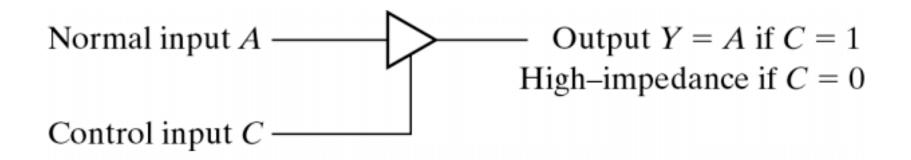

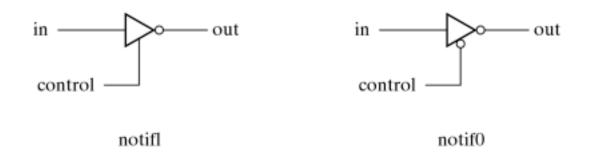

# Multiplexer Via Three-State Gates

(b) 4 - to - 1 line mux

Fig. 4-30 Multiplexers with Three-State Gates

#### **Three-State Gates**

Fig. 4-31 Three-State Gates

Fig. 4-32 2-to-1-Line Multiplexer with Three-State Buffers

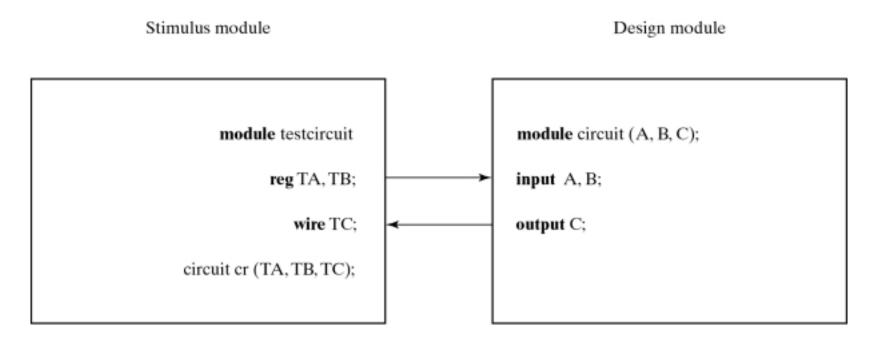

# Stimulus and Design Modules Interaction

Fig. 4-33 Stimulus and Design Modules Interaction