# **Important formulae and device models for you to prepare for ELE2110A test 2**

Prof. KP Pun, 13 March 2008

BJT collector current in active mode:  $i_C = I_S e^{v_{BE}/V_T}$

BJT collector current in active mode (including Early effect):  $i_c = I_s e^{v_{BE}/V_T} (1 + \frac{V_{CE}}{V_A})$ Relationship between base and collector currents for BJT in active mode:  $i_B = \frac{i_c}{\beta}$ Relationship between emitter and collector currents for BJT in active mode:  $i_c = \alpha i_E$ Relationship between  $\alpha$  and  $\beta$ :  $\alpha = \frac{\beta}{1+\beta}$ Single stage BJT amplifier properties:

|                          | C-E<br>(R <sub>E</sub> =0) | Emitter Degenerated<br>C-E | C-C                          | C-B                      |

|--------------------------|----------------------------|----------------------------|------------------------------|--------------------------|

| Terminal<br>Voltage Gain | Inverting<br>& large       | Inverting & moderate       | 1                            | Non-inverting &<br>Large |

| Input<br>Resistance      | Moderate                   | Large                      | Large                        | Low                      |

| Output<br>Resistance     | Moderate                   | Large                      | Low                          | Large                    |

| Input Voltage<br>Range   | Small                      | Moderate                   | Large                        | Moderate                 |

| Terminal<br>Current Gain | Inverting<br>& Large       | Inverting & Large          | Non-<br>inverting &<br>Large | 1                        |

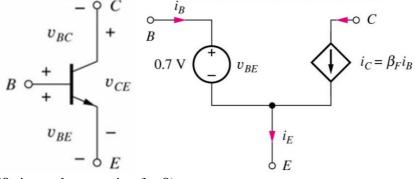

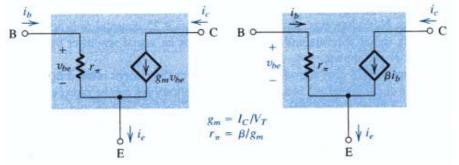

### Simplified DC model for *npn* transistor in active mode:

$(\beta_F \text{ is another notation for } \beta).$

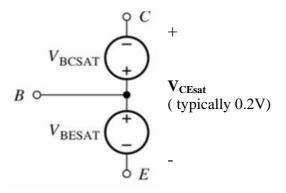

### Simplified DC model for *npn* transistor in saturation mode:

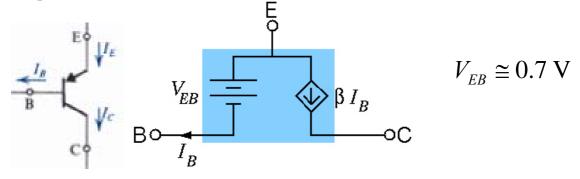

Simplified DC model for *pnp* transistor in active mode:

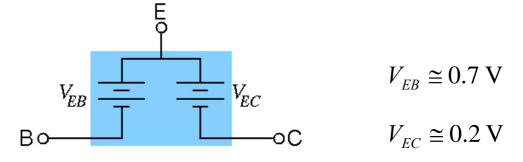

Simplified DC model for *pnp* transistor in saturation mode:

Small signal AC model for BJT (both *npn* and *pnp*) in active mode (Hybrid- $\pi$  model):

Constraint on  $v_{be}$  for BJT small signal models to be valid:  $v_{be} <\!\!< V_T$  (thermal voltage)

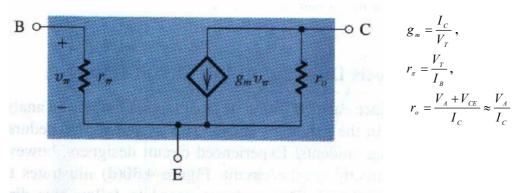

### Hybrid- $\pi$ model including $r_0$ :

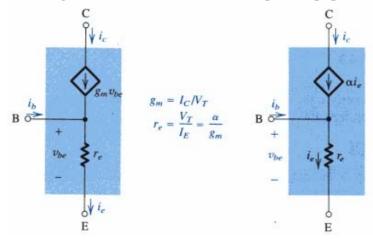

Small signal AC model for BJT (both *npn* and *pnp*) in active mode (T-model):

| Region       | Cutoff                    | Triode                                                                                       | Saturation                                                    |  |

|--------------|---------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| Conditions   | $v_{GS} < V_t$            | $v_{GS} \ge V_t$                                                                             |                                                               |  |

| Conditions   |                           | $v_{DS} < v_{GS} - V_t$                                                                      | $v_{DS} \ge v_{GS} - V_t$                                     |  |

| I-V relation | <i>i</i> <sub>D</sub> = 0 | $i_{D} = K'_{n} \frac{W}{L} \left[ (v_{GS} - V_{t}) v_{DS} - \frac{1}{2} v_{DS}^{2} \right]$ | $i_{D} = \frac{1}{2} K'_{n} \frac{W}{L} (v_{GS} - V_{t})^{2}$ |  |

n-channel MOSFET I-V equations in different modes:

where  $K_n = \mu_n C_{ax}$ , V<sub>t</sub> is the threshold voltage (sometimes denoted as V<sub>TN</sub> for nmos).

## Saturation mode equation including the channel length modulation effect:

$$i_D = \frac{K_n}{2} \frac{W}{L} \left( v_{GS} - V_t \right)^2 \left( 1 + \lambda v_{DS} \right)$$

### p-channel MOSFET I-V equations in different modes:

| Cutoff                                                 | -<br>Triode/Linear                                                      | Saturation                               |  |  |  |  |

|--------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------|--|--|--|--|

| $i_D = 0$                                              | $i_D = K_p \left[ (v_{GS} - V_t) v_{DS} - \frac{1}{2} v_{DS}^2 \right]$ | $i_D = \frac{1}{2} K_p (v_{GS} - V_t)^2$ |  |  |  |  |

| where $K_n = K_n' \frac{W}{T}$ , $K_n' = \mu_n C_{ar}$ |                                                                         |                                          |  |  |  |  |

where  $K_p = K_p \frac{W}{L}$ ,  $K_p = \mu_p C_{ox}$

$V_t$ ,  $v_{GS}$  and  $v_{DS}$  are negative for pmos.

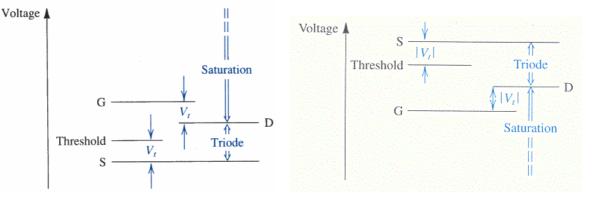

### Charts helping you to judge the operational mode of nmos (left) and pmos (right):

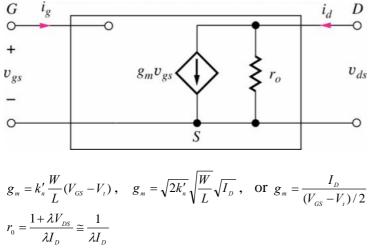

#### MOSFET small signal model (for both nmos and pmos):

Constraint on  $v_{gs}$  for the small signal model to be valid:  $v_{gs} \ll 2(V_{GS} - V_t)$ , or  $v_{gs} \ll 0.2(V_{GS} - V_t)$ .